- 非IC关键词

企业档案

- 相关证件:

- 会员类型:普通会员

- 地址:深圳市福田区华强北赛格科技园四栋中12楼A4座―2L

- 传真:0755-83955172

- E-mail:1282971461@qq.com

产品分类

相关产品

产品信息

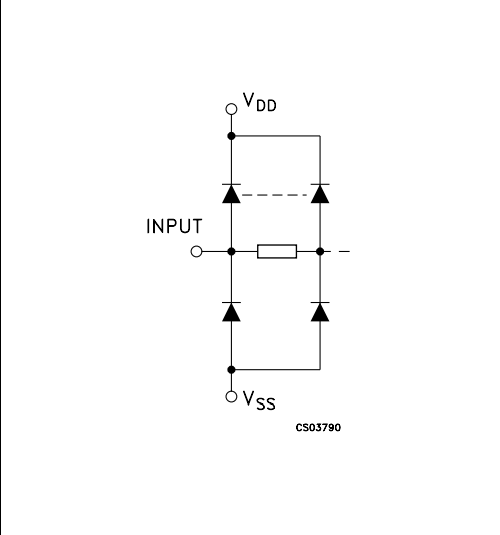

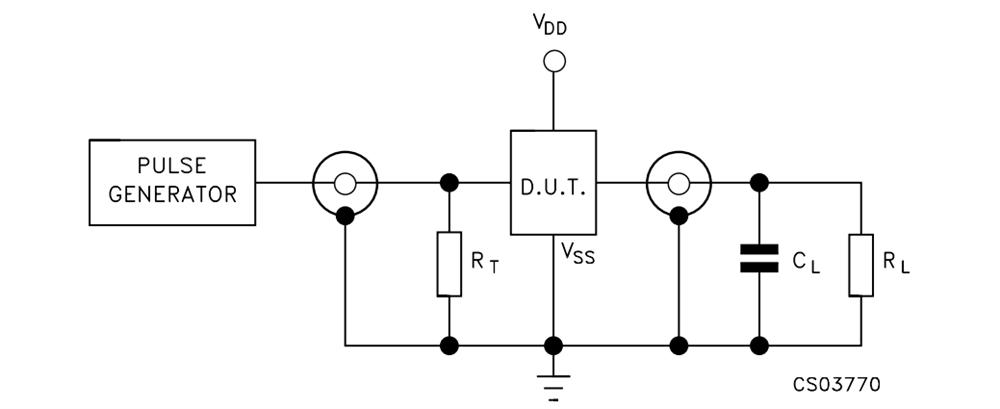

LOW "ON" RESISTANCE : 125Ω (Typ.)

OVER 15V p.p SIGNAL-INPUT RANGE FOR

VDD - VEE = 15V

■ HIGH "OFF" RESISTANCE : CHANNEL

LEAKAGE ± 100pA (Typ.) at VDD - VEE = 18V

■ BINARY ADDRESS DECODING ON CHIP

■ HIGH DEGREE OF LINEARITY : < 0.5%

DISTORTION TYP. at fIS = 1KHz, VIS =5Vpp,

VDD - VSS > 10V, RL = 10KΩ

■ VERY LOW QUIESCENT POWER

DISSIPATION UNDER ALL DIGITAL

CONTROL INPUT AND SUPPLY

CONDITIONS : 0.2 μW (Typ.)

at VDD - VSS = VDD - VEE =10V

■ MATCHED SWITCH CHARACTERISTICS :

RON = 5Ω (Typ.) FOR VDD - VEE = 15V

■ WIDE RANGE OF DIGITAL AND ANALOG

SIGNAL LEVELS : DIGITAL 3 to 20,

ANALOG TO 20V p.p.

■ QUIESCENT CURRENT SPECIF. UP TO 20V

■ 5V, 10V AND 15V PARAMETRIC RATINGS

■ INPUT LEAKAGE CURRENT

II = 100nA (MAX) AT VDD = 18V TA = 25°C

■ 100% TESTED FOR QUIESCENT CURRENT

■ MEETS ALL REQUIREMENTS OF JEDEC

JESD13B " STANDARD SPECIFICATIONS

FOR DESCRIPTION OF B SERIES CMOS

DEVICES"

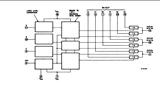

When a logic "1" is present at the inhibit input

terminal all channel are off. This device is a triple

2-channel multiplexer having three separate

digital control inputs, A, B, and C, and an inhibit

input. Each control input selects one of a pair of

channels which are connected in a single pole

double-throw configuration.

HCF4053M013TR 半导体 多路复用开关IC 2-ChHCF4053M013TR 半导体 多路复用开关IC 2-Ch

HCF4053M013TR 半导体 多路复用开关IC 2-Ch

HCF4053M013TR 半导体 多路复用开关IC 2-Ch

询价

询价